分解的设计对于未来的处理器、GPU和其他芯片将变得越来越重要。AMD已经将这种小芯片策略用于Ryzen处理器,英特尔将与Meteor Lake和Sapphire Rapids一起做到这一点,而AMD和NVIDIA的GPU迟早也会由几个芯片组成。

去年,IBM在Hotchips 33上推出了z16 Telum。该处理器实际上由两个芯片组成,每个芯片有八个内核,32 MB的L3缓存以及一个容量分别为256 MB的通用L3和L4缓存,虚拟2 GB超过八个处理器。它们在台积电采用7 nm制造,并配有225亿个晶体管,面积为530 mm²。其中两个芯片在封装上工作,它们相互连接。

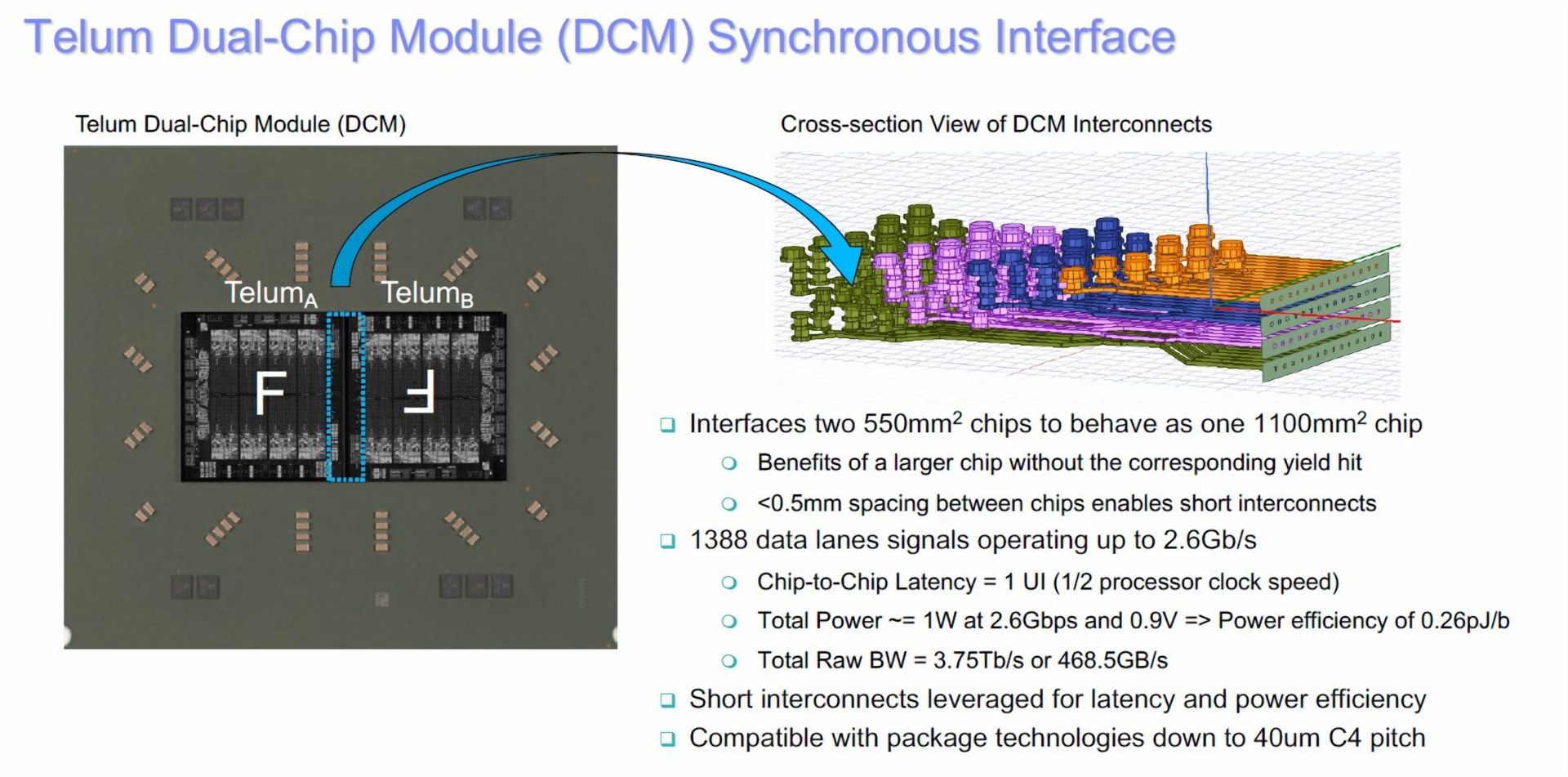

正是在这方面,设计的真正挑战在于,因此两个小芯片像处理器一样呈现在外部。IBM开发了双芯片模块(DCM)同步接口,当然也可以与竞争对手的解决方案进行比较。Twitterer和分析师Dylan Patel已经发现了有关此事的一些信息。

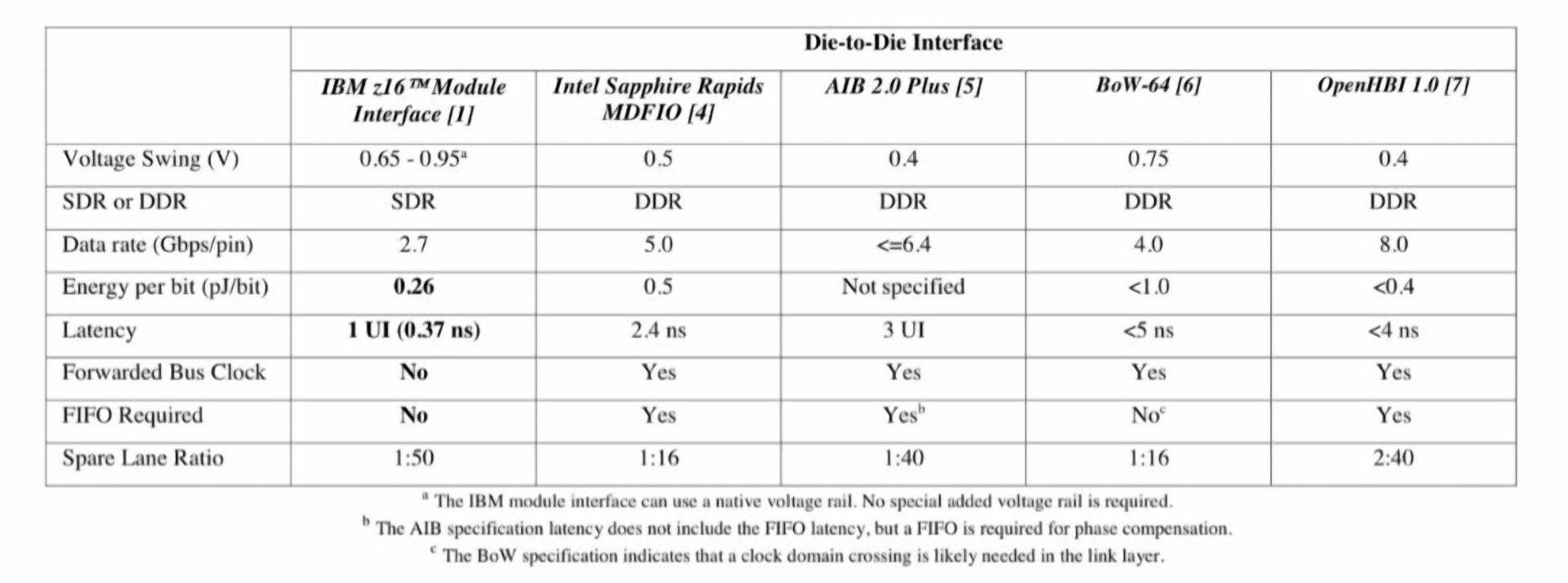

IBM的芯片接口与英特尔的MDFIO进行了比较,因为它将用于即将推出的Xeon处理器Sapphire Rapids。还比较了英特尔开发的高级接口总线(AIB)以及BoW-64和OpenHBI。

例如,IBM 的模块接口使用 SDR(单一数据速率)而不是 DDR(双倍数据速率)。因此,每个时钟周期只传输一个位,而不是两个。当然,每个引脚的数据速率只有其一半。然而,突出的是传输效率。IBM只有0.26 pJ /位,而0.5 pJ /位的MDFIO每次传输所需的能量是一位的两倍。因此,互连在 2.6 GBit/s 时的功耗为 1 W。原始带宽为 468.5 GB/秒。

第二个令人惊讶的事实是IBM在芯片之间实现的延迟。这里应该是0.37 ns,而英特尔是2.4 ns。这主要对数据的行为和交换产生影响,因为这两个芯片旨在充当一个处理器。

芯片之间总共使用了1,388个数据连接。使用DDR进行信号传输时,它们的数量会略小,但IBM选择了这条道路。其中一个原因可能是IBM不需要任何类型的连接的任何桥接器或转接板材料 - 因此生产中的工作量应该受到限制。总而言之,这是对IBM技术和实现的有趣见解。

| 欢迎光临 Chiphell - 分享与交流用户体验 (https://www.chiphell.com/) | Powered by Discuz! X3.5 |