再加上新的玻璃基板?

再加上新的玻璃基板?

升级又有盼头了,AMD YES

升级又有盼头了,AMD YESfinished 发表于 2024-11-29 20:17

本来满血就是32c,都怪牢英不给力,不然早出来了。

24c而已

pzy2222 发表于 2024-11-29 20:40

变化这么大,还能用AM5么

yhwy 发表于 2024-11-29 20:26

啊?我去搜搜,zen3x3d才开始关注的,还有这么些历史的?

panzerlied 发表于 2024-11-29 22:43

这是折中的方案吗,8C和16C折中一下变成12C。

finished 发表于 2024-11-29 21:37

5000 还是7000系时候的事,当时都报道传闻有32c的工程样品,然后就不了了之了。很明显对付牢英一只手就够 ...

pcgsf22 发表于 2024-11-29 21:49

内存带宽不够加核心有啥用,只是提高了12核u的性能罢了

pcgsf22 发表于 2024-11-29 21:49

内存带宽不够加核心有啥用,只是提高了12核u的性能罢了

8xwob3ko 发表于 2024-11-29 11:26

高带宽方案一直有现成的,压成本不肯下放才是问题

赫敏 发表于 2024-11-30 01:16

就算不计成本,也要计功耗吧。现在epyc计算跟互联的功耗基本对半开,要更多核心的低延迟互联功耗和面积只 ...

赫敏 发表于 2024-11-30 01:16

就算不计成本,也要计功耗吧。现在epyc计算跟互联的功耗基本对半开,要更多核心的低延迟互联功耗和面积只 ...

af_x_if 发表于 2024-11-29 20:21

32c是mesh?

赫敏 发表于 2024-11-30 01:16

就算不计成本,也要计功耗吧。现在epyc计算跟互联的功耗基本对半开,要更多核心的低延迟互联功耗和面积只 ...

panzerlied 发表于 2024-11-29 22:43

这是折中的方案吗,8C和16C折中一下变成12C。

大头吃小头 发表于 2024-11-29 22:53

16c怎么解决延迟问题啊

intel 8+16(4个簇) 还各种翻车

16个大核不是双ccx估计要翻车的感觉

af_x_if 发表于 2024-11-30 07:30

我猜测下

Zen6型号是10、12、20、24核,用新命名系统,可能就是460、470、490、495。

Zen5可能Refresh一下 ...

赫敏 发表于 2024-11-30 20:37

前提是MLID靠得住

KimmyGLM 发表于 2024-11-30 12:53

比起核心数,更关心if带宽能不能继续扩大,以及主板南桥的小水管能不能向带英看齐 ...

快进到AMD R5 *500X3D秒intel ultra 9

快进到AMD R5 *500X3D秒intel ultra 9fengpc 发表于 2024-12-1 09:54

自己不做南桥找的祥硕订制的南桥芯片,没法看齐的,AMD平台小问题多多工控厂家都不敢用 ...

BMeteor 发表于 2024-12-1 09:26

zen6 IPC常规提升,换iodie,CCD加到12C,3DL3变96m,我都不知道劳英怎么赢

netjunegg 发表于 2024-11-30 14:18

我觉得pc平台总线带宽上也有必要差异化了, 跟苹果类似, 中端带宽比低端翻倍, 高端又比中端翻倍, 相当合理 ...

叶子烟 发表于 2024-11-29 20:49

DDR6没出来的话,不用AM5用啥

8xwob3ko 发表于 2024-11-30 00:28

现在内存带宽瓶颈都是IF总线,下一代大概率也要换的,就是这省成本的样子也不太可能一步到位硅互联 ...

kingofgu 发表于 2025-2-4 04:40

Strix Halo已经换了 新的4nm iodie加直接扇出

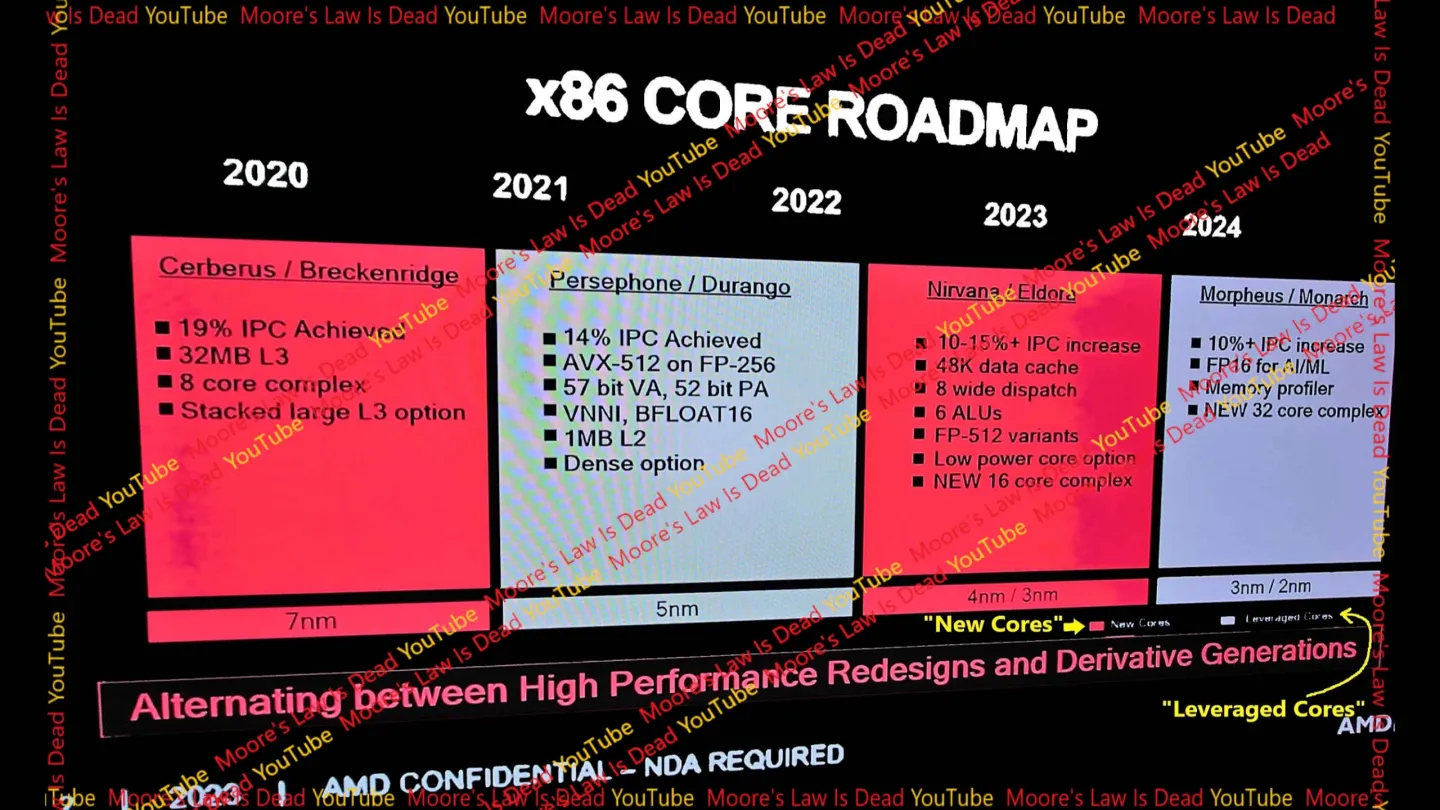

消息称除了“Medusa Ridge”之外,AMD 还计划在代号为“Venice”的下一代 EPYC 处理器、Medusa Point / Medusa Halo 移动处理器中也采用全新 CCD。

| 欢迎光临 Chiphell - 分享与交流用户体验 (https://www.chiphell.com/) | Powered by Discuz! X3.5 |