|

|

本帖最后由 我輩樹である 于 2025-2-10 15:38 编辑

不是自媒体,卖超算工作站的商家。

https://forums.anandtech.com/thr ... ns-welcome.2621420/

这里也有人说9124是4ccd。

搜9124感觉这个u的问题挺多。

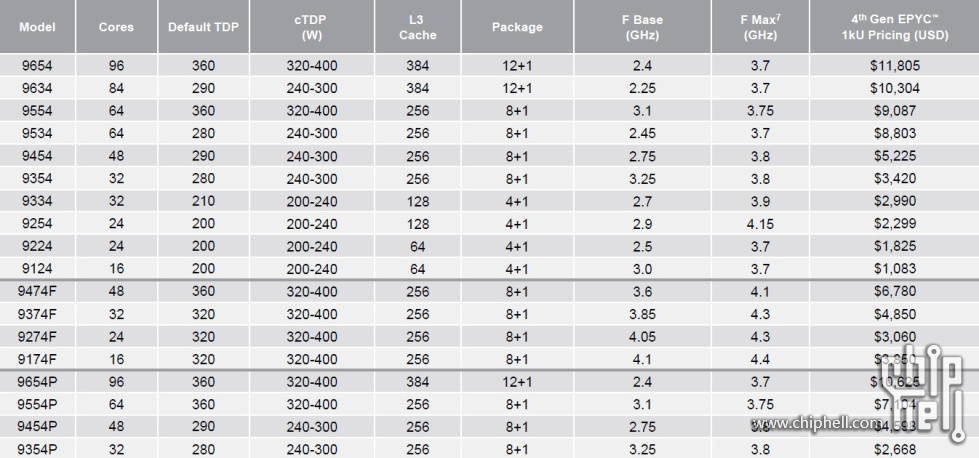

有找到了点资料,9124/9224确实是2个例外:

https://www.cfd-online.com/Forum ... yers-guide-cfd.html

3. Pitfalls and CPUs to avoid

Just like in the previous generations, the connection between the compute dies (CCD) and the I/O-die where the memory controllers reside can be a bottleneck. For 2nd gen Epyc Rome, we had CPUs with effectively half the total memory bandwidth thanks to this bottleneck.

The GMI3 links between CCD and an IOD did not undergo major changes. If my napkin math is correct, the bandwidth here is 57.6GB/s and 22.8GB/s for read and write respectively. Which requires 8 of these links to match the memory bandwidth. Remember: reads are more important than writes in most cases, so it doesn't matter that the write bandwidth lacks behind.

AMD has a trick up their sleeve: the CPUs with only 4 CCDs can be connected to the IOD with 2 GMI3 links each, which is enough to utilize the full potential of the memory subsystem. So in theory, the full stack of CPUs launched so far should not hide any nasty surprises.

CAVEAT: should

The wording in AMDs official slides is not definitive enough for my personal taste. It is stated that CPUs with 4 CCDs can utilize 2 GMI3 links per CCD. Not that all of them necessarily do. Maybe I'm just too paranoid, decide for yourself...

And there are the 2 low-end CPUs with only 64MB of L3 cache. How this is achieved remains to be seen. Up until now, 64MB L3 cache on an Epyc CPU meant only 2 CCDs are active. Which wasn't enough to get the full bandwidth in previous generations, and still isn't enough in this generation, even with two GMI3 links per CCD. The table above lists them as 4 CCD parts. AMDs official website lists all CPUs with a memory bandwidth of 460.8GB/s. But until detailed benchmarks for some of the lower-end parts are out, I would treat that information with some skepticism.

Edit: after sifting through AMD's own technical documentation, I can confirm that ALL CPUs launched so far consist of at least 4 active CCDs. Even those with 64MB of L3 cache.

Regardless, the value proposition for the lowest-end SKUs 9224 and 9124 just isn't there. The platform cost is fairly high thanks to PCIe5 and DDR5. And the halved L3 cache will have a negative performance impact. In this price and core count range, you are likely better off with some discounted parts from previous generations.

And until further benchmarks or confirmations are available, I reserve final judgement for all all SKUs listed above with a "4+1" configuration. I will post an update if/when that happens.

它们虽然是4ccd,但l3太小了,所以这些搞cfd的人不推荐 。 。

|

|

310112100042806

310112100042806