本帖最后由 PPXG 于 2024-8-31 22:40 编辑

首先我假设各位对intel处理器的供电机制有一个比较详细的了解,前置内容基础为隔壁论坛网友 嗯嗯嗯嗯什么 的帖子《LGA1700(英特尔12代13代14代)核心供电机制和ACLL机制解析》(链接:https://nga.178.com/read.php?tid=38739235)

或者buildzoid的视频《How load line calibration actually works》(链接:https://www.youtube.com/watch?v=bUaP0r5-xhY)

顺带一提,在我写这个帖子期间,buildzoid刚好在油管直播Loadline机制来着,不过完帖之前直播已经结束,不知道会不会有回放

如果不想看那么长的帖子的话(我还是建议看一下的),这里简单省流一下本帖可能会用到的内容:

这里有一个CPU,在有负载的瞬间,电压会突然猛掉一下然后再升回来,称为V undershoot;在负载结束的瞬间,电压会突然猛冲高一下然后再降回去,称为V overshoot。

我们来解决V undershoot:

CPU的原始VID(出厂时就写死在CPU里的,无法更改,华硕主板可以通过高级模式 -> AI Tweakwer -> V/F Point Offset 内的菜单找到原始VID表)经过一系列的计算得到一个和原始VID略有偏差的实时VID。

对于一个特定负载来说,因为物理电阻的存在导致必然会出现不可避免的掉压现象(CPU向VRM请求的电压等到达CPU里就不是那个电压了,会变低),那么有没有什么办法去解决这个问题呢?这时候AC Loadline就出现了:CPU猜测自己接下来的负载会使用到多少电流,这个东西叫预测电流,然后去乘上VRM到CPU之间的等效电阻——这个等效电阻由AC Loadline的值决定,单位为毫欧姆mOhm。U=I * R,这就是会掉的电压幅度,那么CPU接下来请求的电压在实际VID的基础上再加上这个值,那么掉压之后电压和以前空载时一样安全,完美!注意:这个等效电阻一般人很难测试出来结果,而主板之间的体质差异甚至一些未在出厂前检测出来的潜在缺陷也可能会造成即使同一型号主板不同个体间的实际等效阻值不尽相同。不过通常认为,越高端的主板供电设计和用料越好,等效阻值也会越低。

但是只有ACLL存在的话,CPU在进入负载掉压之后,VRM会尝试再把电压加回去,就会出现负载电压比空载电压还高的可笑情况。这时候,就需要引入VRM Loadline:VRM根据实际电流 控制电压,具体下降幅度为实际电流乘VRM到CPU之间的等效电阻——这个等效电阻由VRM Loadline的值决定,单位为毫欧姆mOhm。

这时候你会发现,我还没提到怎么解决V overshoot?

很遗憾,V overshoot 无法完全消除。V overshoot需要依靠主板的供电能力去尽可能的最小化:比如供电的响应速度越快,越能尽快的抑制住电压并调节回来;再比如供电的储能系统如电容越大,越能延缓电压上升的速度。。。。。。

而主板供电性能是如何和ACLL VRMLL关联起来的呢?

我们认为一个理想的ACLL VRMLL应该刚好匹配主板应对V undershoot和V overshoot的情况:

如果ACLL太低,由于升压程度不够,电压依然可能会下探到低于处理器稳定工作的电压,这时候你需要升高基础VID电压(比如正向offset核心电压),可能出现空载轻载电压偏高的情况,当然问题似乎也不是很大,并且本帖不打算深入探讨ACLL问题。

但是如果VRMLL太高,因为VRMLL会根据实际电流去调节,会导致电流变化前后VRM调控的电压差异巨大,甚至远大于主板自身供电决定的V undershoot和V overshoot幅度:供电机制引入ACLL和VRMLL的初衷就是尽可能降低V undershoot和V overshoot的影响,那么你把VRMLL无脑调高,是否为一种背离该机制初衷的行为?

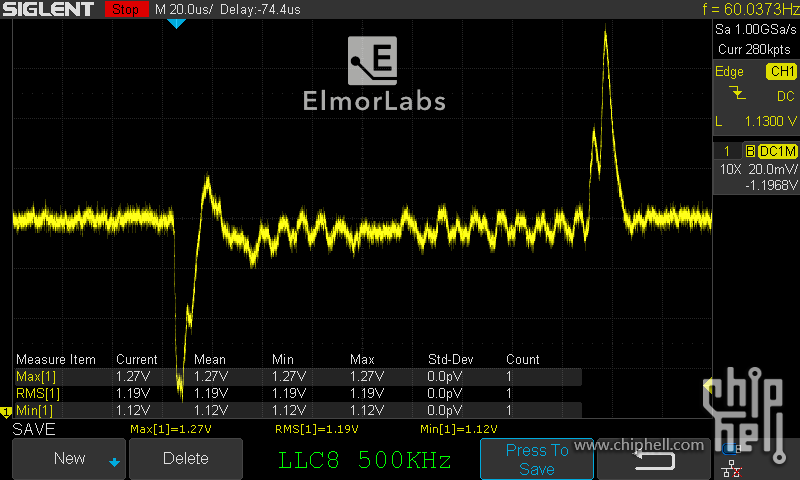

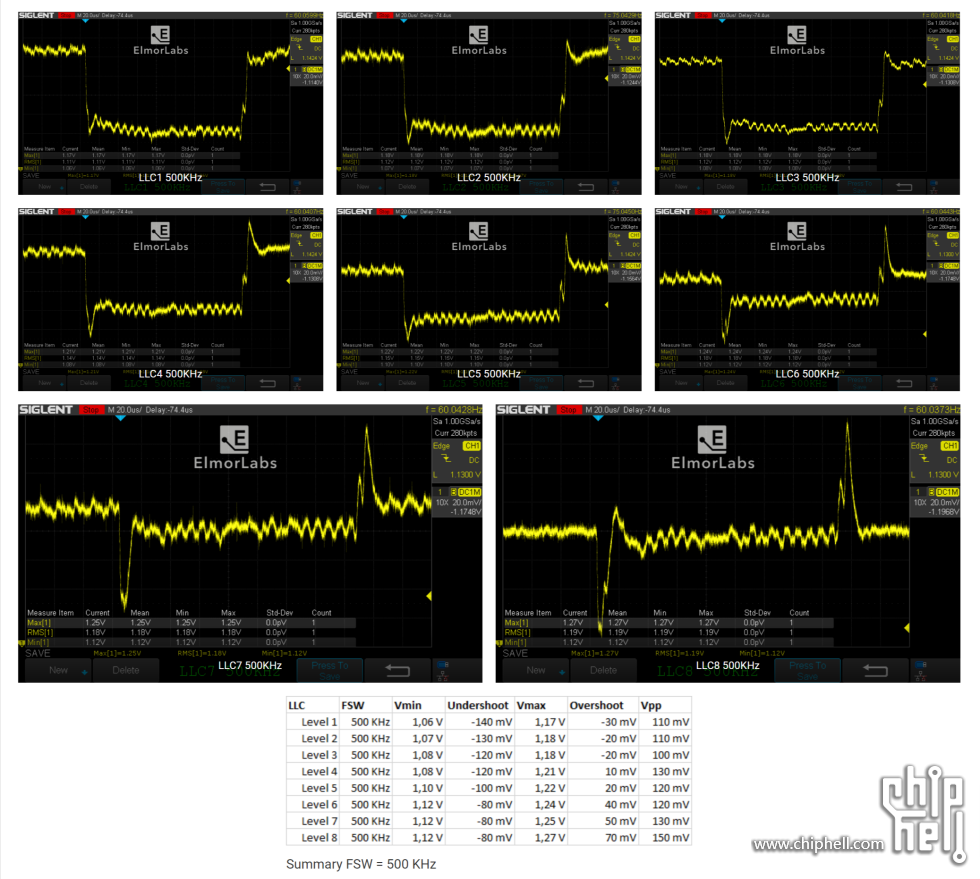

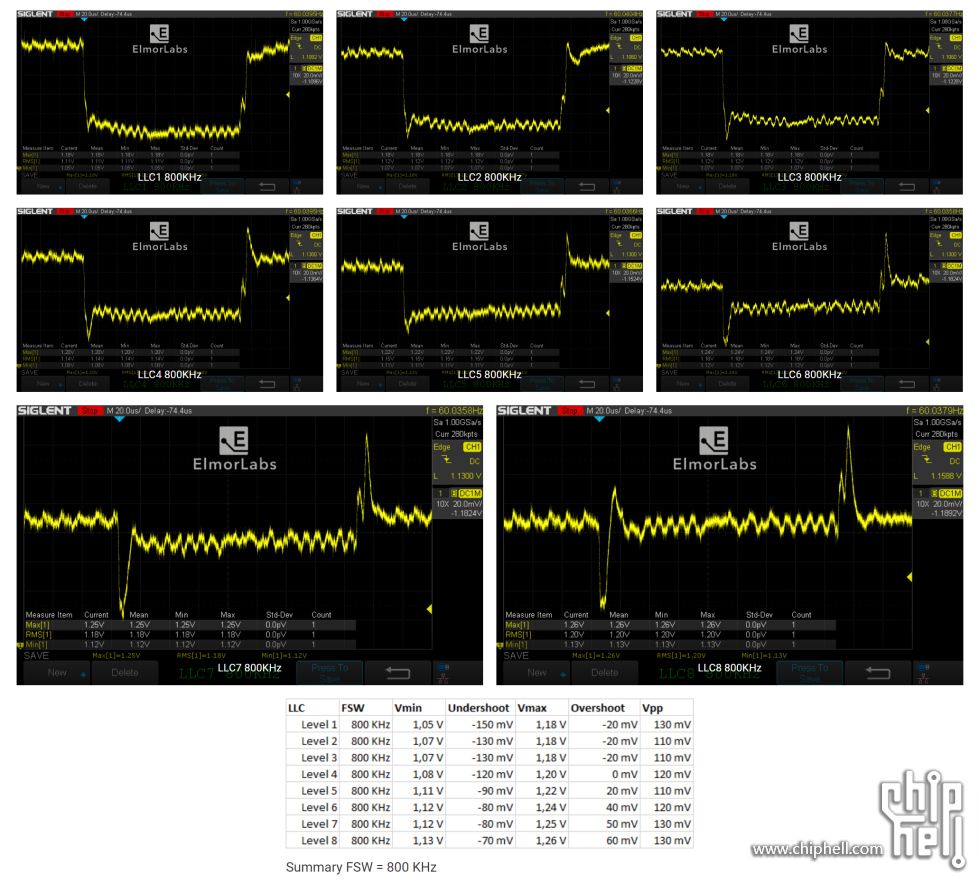

在Elmorlabs的文章《VRM Load-Line Visualized》(链接https://elmorlabs.com/2019-09-05/vrm-load-line-visualized/)中,作者用示波器测试并展示了不同VRMLL档位下的电压变化区别,可以看到Loadline Calibration并不是档位越高越好,对于图中的主板(ROG Maximus XI Gene )来说,LLC Level3能最小化V undershoot和V overshoot的影响(Vpp 最小)。而对于LLC Level1这种极端的档位来说,Vpp值并不是最完美的,并且V undershoot更为严重,尤其是在800KHz的VRM开关频率下:

LLC1 截图说明了理想的负载线行为。随着负载线值的降低(更高水平),线路变得平坦,开始和结束时的下冲/过冲尖峰变得更加明显。负载瞬变开始时的最低电压点并没有太大改善。在这种情况下,使用高于 3 的负载线水平似乎值得怀疑。负载电压会增加,意味着功耗更高,但最坏情况下的最低电压会保持不变。此外,负载释放后的过冲也会增加。将 VRM 开关频率从 500 KHz 增加到 800 KHz 显示出非常小的改进。

所以结论很显然,ACLL和VRMLL并不是无脑越高或者越低越好:他们更应该尽可能的匹配主板的实际供电性能,最小化的消除V undershoot和V overshoot对运行稳定性的影响。

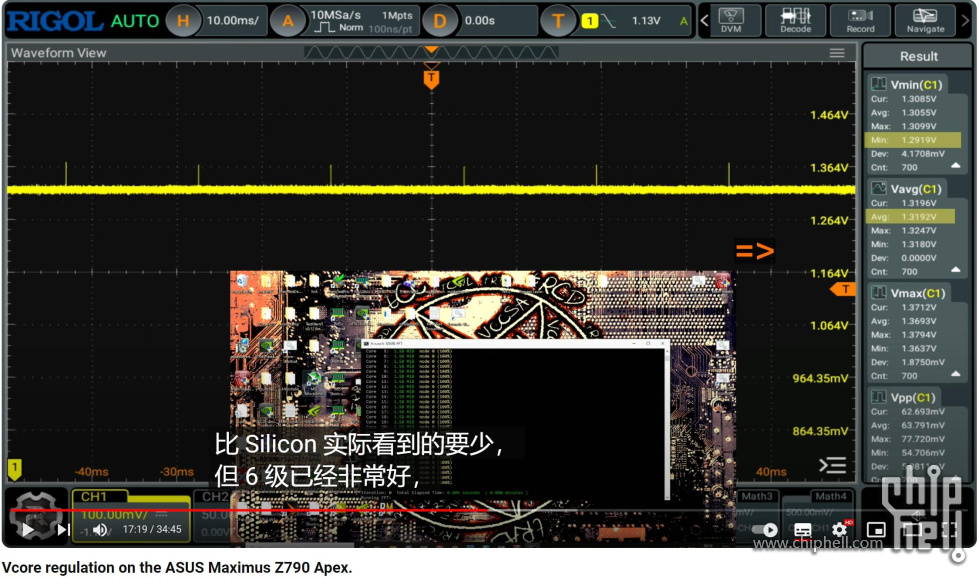

极客湾视频中提到的LLC Level6是一个比较小的数值:对于华硕来说,LV6对应的VRMLL为0.49mOhm,根据油管频道“Actually Hardcore Overclocking”的视频《Vcore regulation on the ASUS Maximus Z790 Apex》(链接:https://www.youtube.com/watch?v=bNhcdwfvgLY),他通过实际运行负载并通过示波器测量实际欠压和过冲情况,认为对于他手里的这张Z790 Apex来说,LV6是最合适的

主板适合更低的VRMLL,说明主板的供电性能越强,越能在负载变动时更快速的调节电压,降低过冲和欠压的幅度。而对于其他主板比如Z790吹雪、B760M重炮手来说,他们的供电性能显然不可能有Apex那么强,这时候用LLC档位4或者5可能是比较契合主板供电性能的。

而华硕的防掉压LV1是另一个极端数值:VRMLL此时被设置为1.76mOhm,比intel推荐规范还要高出60%。我实在是想不出到底多烂的主板才会不得不使用这个数值,至少我不认为华硕微星技嘉的支持超频的主板供电性能会烂到这种程度。而且按照VRMLL的机制来说,此时即使一个造成持续电流200A的负载(对于13900K这个级别的处理器来说,这种电流应该还是蛮常见的)都可能会造成高达350mV的电压调控变化,防掉压无脑开到这种程度,真的OK?

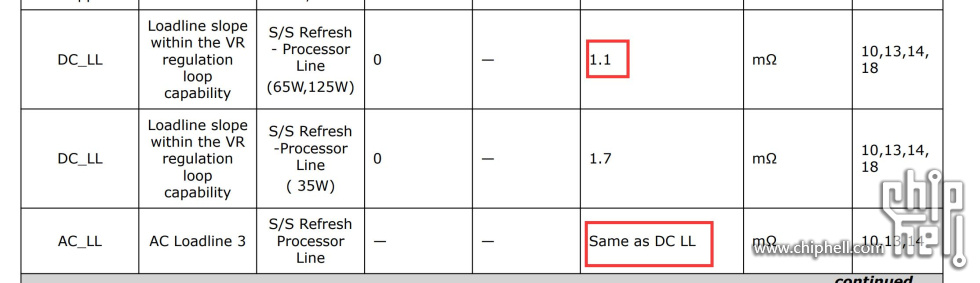

顺带一提,即使是intel自己的《13th Generation Intel® Core™ and Intel® Core™ 14th Generation Processors Datasheet》里,RPL-S正常桌面型号规定的AC_LL和DC_LL值就是1.1mOhm,这还是考虑到有些主板供电性能比较烂的情况。你让别人不看主板无脑去设置一个Level 1,开机一开1.76mOhm,不是纯放屁?

不了解主板供电机制就在论坛和B站大放厥词,甚至说出“AC、DC Load Line和 Offset效果是一样的”这样的话,不是纯放屁?

最后,附上华硕主板不同档位对应的VRMLL:

Level 1 , 1.76 mOhm

Level 2 , 1.49 mOhm

Level 3 , 1.10 mOhm

Level 4 , 0.98 mOhm

Level 5 , 0.73 mOhm

Level 6 , 0.49 mOhm

Level 7 , 0.24 mOhm

Level 8 , 0.01 mOhm

ACLL DCLL可以通过hwinfo64 主界面 -> 中央处理器 -> 点击你的CPU,右侧下滑找到“IA Domain Loadline (AC/DC) ”获取,对于绝大多数主板来讲,默认DCLL和VRMLL同步,此处DCLL就是VRMLL |

310112100042806

310112100042806