土星实验室 发表于 2022-11-5 21:06 要是P3顶的住,用的着慌慌张张的上马P4还成了笑话? Athlon不说碾压P3,也可以说全面超越,频率上P3更是完败,率先让AMD拿下1G,虽说后来的图拉丁改善了局面,但雷鸟的祭出图拉丁完全跟不上,才不得不上马P4拼频率。 |

T.JOHN 发表于 2022-11-5 15:55 为何会减少2个大核心? |

koney 发表于 2022-11-6 19:35 这话去跟按摩店和牙膏厂的首席架构工程师说,问他们为什么要用密度最低的高性能库去造大核,为什么要出厂就电到1.3v以上,我可是跑1.0v出头的古典派。 |

| 对了,那么喜欢ppa建议去用只有a53。再不然直接把牙膏买下来,下令用18a hp library搞个Conroe refresh,ppa之强保证连水果都甘拜下风,至于什么zen4还是GLC连提鞋都不配。只要规模不堆上去然后只更新制程,ppa一定是最强的。 |

5d5588cf 发表于 2022-11-6 19:28 哪有您牛逼啊,ppa,能耗比,chiplet这些在您眼中想必还不如跑高频有价值, 真的是领先业界的理解啊 |

koney 发表于 2022-11-6 19:15 大师真是牛逼,有本事用hp library造出能跑5.3GHz的GLC,牙膏都要用uhp library才行。zen2和zen4的数据上面不是写了?zen2和zen4就不是zen?还是大师靠着高考阅读理解0分进的MIT EE? |

5d5588cf 发表于 2022-11-6 18:56 美食家都得有特技厨师证书是吧,那以后测评员都必须持mit ee博士证书测评是吧 |

5d5588cf 发表于 2022-11-6 17:15 同系列架构纵向对比还对比出优越感了  ,怎么不横向对比下其他架构,既然gdc这么牛逼intel为啥要用gracemont来补ppa。你再对比下zen,fs,甚至arm,看看增加了多少晶体管,提升了多少ipc ,怎么不横向对比下其他架构,既然gdc这么牛逼intel为啥要用gracemont来补ppa。你再对比下zen,fs,甚至arm,看看增加了多少晶体管,提升了多少ipc |

liyichao97 发表于 2022-11-6 17:29 在那位大师的眼中SKL也是垃圾,毕竟用2%晶体管换1% ipc就是ppa垃圾,正常的架构都是1%晶体管换2%的ipc,建议那位大师拿着他的MIT电子工程博士证书去按摩店或者牙膏厂应征首席架构工程师。 |

土星实验室 发表于 2022-11-5 21:06 k7 比 p3 先过 1GHz 的 |

5d5588cf 发表于 2022-11-6 17:15 skylake就很好啊,14nm的密度那么差却实现了这性能,ipc跟7nm的zen2有来有回,按晶体管数计算的性能效率跟gracemont比也差不了太多 |

本帖最后由 5d5588cf 于 2022-11-6 18:58 编辑 koney 发表于 2022-11-6 10:34 所以按照你的定义过去10年市面上从x86到arm全部架构的ppa都是垃圾,提升多了就是上一代垃圾,提升少了就是这一代垃圾,你说的都对。 |

dychenyi 发表于 2022-11-5 21:41 ccd卡着甜点面积做的,真要搞100多mm^2 良率下来,制造成本就上去了。 而且做mask 也贵,上亿美金, zen4 产量上不去要亏钱的。 intc自己搞mask能省不少钱, 制造成本高点也能接受 |

dychenyi 发表于 2022-11-5 19:44 int4 可不行,intc自己说工艺领先得20a/18a, 得25年了 |

texnis 发表于 2022-11-5 16:50 3fin 密度本来就低,加上sram 密度也上不去 93mtr已经很高了 |

5d5588cf 发表于 2022-11-6 03:49 真牛逼,拿两个ppa都不行的架构来比较。你设计一个ppa很垃圾的架构,完了下一代再设计一个正常的,然后美其名曰没有提升多少晶体管就实现了ipc大幅提升  |

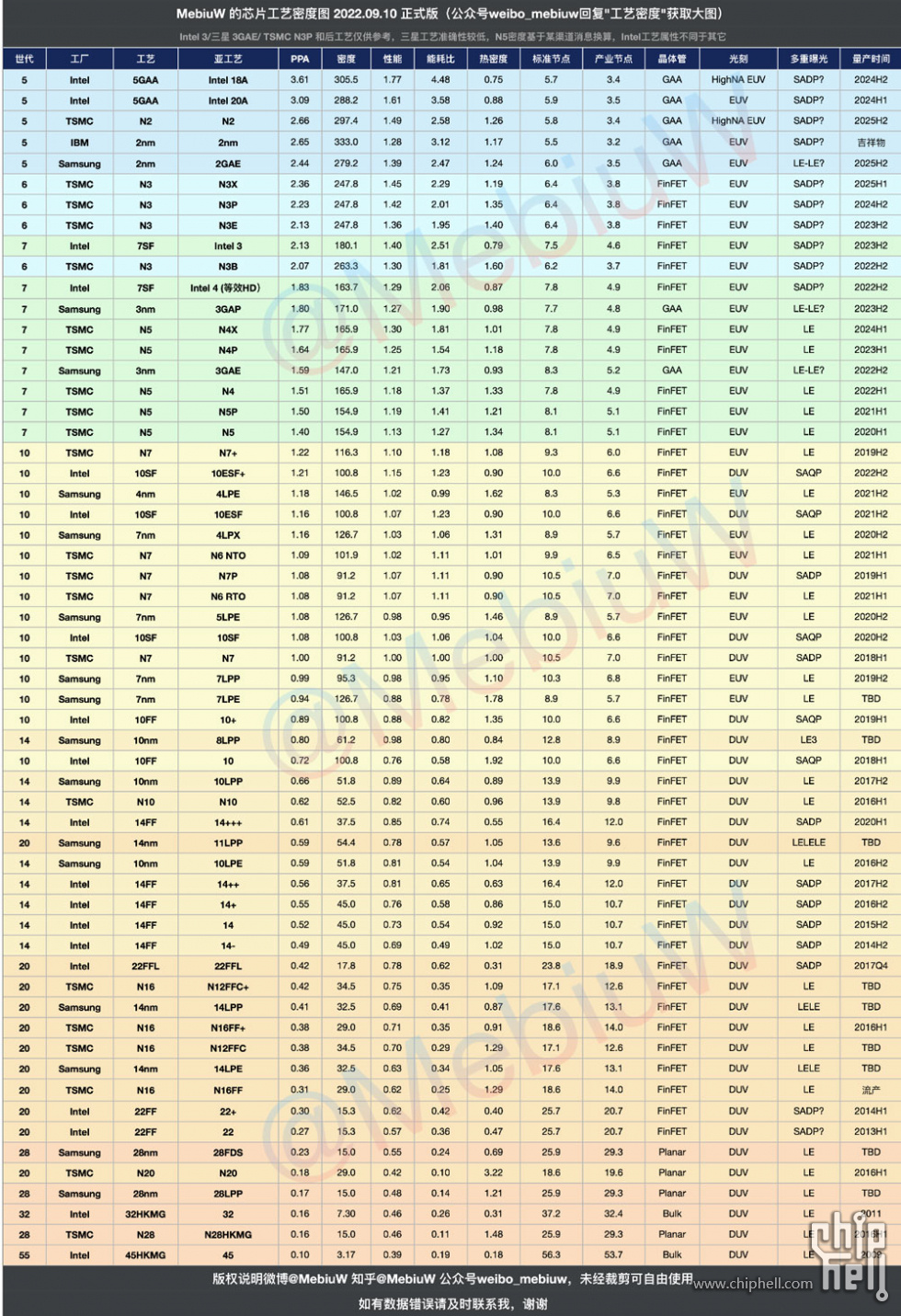

koney 发表于 2022-11-5 17:58 什么叫大力出奇迹?不计算L2和L3的情况下,GLC的晶体管只比WLC多了22-23%情况下多了19% ipc还能叫不牛逼,那么以往平均晶体管多个30-40%的情况下才能多个12-15% ipc又叫什么?过去10年牙膏只有IVB,SNC,GLC这三代可以拉到20%上下,其余的都是连15%都不到。 同样不计算L2和L3的情况下zen2用了26%的晶体管才能比zen多个13-15% ipc,要是跟zen+比还要再少个1-2%,直到zen3才做到了用13%的晶体管换取接近19%的ipc。然而到了zen4情况又回去了,用了超过40%的晶体管换取8-12%的ipc,这还没把zen系减少cache的ipc损失会大于core系的影响考虑进去。 现代cpu架构基本上都是用至少2%的晶体管去换1%的ipc。然而即使如此,在提升同幅度的性能的情况下拉ipc的功耗增幅是低于拉频率,所以绝大部分的架构才会在维持相若的频率为前提下尽可能提升ipc。 |

| 还是感谢AMD吧 |

| 下一代redwood cove传言满天飞,granite rapid用intel 3,meteor lake-U/meteor lake-P用intel 4,meteor lake-s甚至有在传用TSMC N3,鬼知道你在讲哪个…… |

AIAO 发表于 2022-11-5 19:46 哪怕整颗ADL 8+8都是用10ff hd libray都没有亿分之一的可能性超过20B,8+8顶多就14B出头 |

|

膏子的工艺能耗比其实不如台积电的,就是有工厂豪横,把饼子摊大,密度低好散热,所以设计团队在桌面上还能横一下,到了移动端和服务器上也就无能为力了。 有人说膏子=农企+台积电,其实台积电后面站着好多家,苹果老黄高通发哥等等,何止农企一家,膏子工艺确实干不过的,不过现在手机市场也开始疲软出货量下降,膏子也许能翻身?或许pc下滑更猛,膏子万劫不复。。。 |

等东西出来看疗效吧 |

jerrytsao 发表于 2022-11-5 21:02 台积果然还是吹牛了。 DUV换EUV工艺,看起来晶体管密度会有大幅度提升,看来intel下代很值得期待啊。 |

intel最NB的是热密度极低,不会积热。

|

AIAO 发表于 2022-11-5 19:46 查了下,5950X的晶体管数量约为104亿,的确是。 而7950x是160多亿。 IO die分离出来用过低级工艺制造就是省成本的。 有楼层说AMD ccd密度很高,侧面说明intel下代工艺还有的是空间塞更多的吧。 |

AceEX 发表于 2022-11-5 18:17 你这么一说确实有一个因素我没考虑,现在的intel 7工艺相比icelake的10nm放宽太多了 |

yahochina 发表于 2022-11-5 17:56 农企什么时候打过P3了?P4前期农企一样弱鸡,intel在P4失败是后期上高频,流水线太长,IPC没有等效提升 |

|

关于Density, 建议阅读Angstronomics前段时间发的这篇文 https://www.angstronomics.com/p/the-truth-of-tsmc-5nm Intel 7 (Intel 10nm) - Intel列了100.8 MTr/mm², 实际100.3 MTr/mm² TSMC 5nm - 早前WikiChip预计170.6 MTr/mm², 实际137.6 MTr/mm² |

晶体管数量肯定大幅落后 人们只相信自己愿意相信的东西,然而5950X的晶体管数量(1个IO die加2个CCD)约为104亿,12900K有人估算约为200+亿。AMD在成本控制方面一直都有一套。 晶体管数量也说明不了什么,M1/M2的晶体管数量,再看看4090相比3090超过翻倍的晶体管数量。12代/13代其实在工艺方面完全不落后(工艺成本除外),超大规模的ROB还能冲上高频,确实靠的是工艺上的优势。 |

Archiver|手机版|小黑屋|Chiphell

( 沪ICP备12027953号-5 ) 310112100042806

310112100042806

GMT+8, 2025-6-7 05:21 , Processed in 0.015221 second(s), 9 queries , Gzip On, Redis On.

Powered by Discuz! X3.5 Licensed

© 2007-2024 Chiphell.com All rights reserved.