huangfuda 发表于 2024-6-12 18:22 更先进,所以可以降低。 降低电压的理由可能是新制程电压上限更低,也可能是新制程能效更好所以降压省功耗。 至于具体到DDR5和DDR4 JEDEC电压从1.2降到1.1,只是为了省功耗。 而DDR2到DDR3从1.9降到1.5可能就是工艺不再支持最高1.9的电压了。 |

bigeblis 发表于 2024-6-12 18:28 现代的器件工作条件更接近这种情况 下降到低于0.4V逻辑0, 上升到高于0.6V逻辑1, 中间亚稳态 1V下, 上升率1ns/V, 0.4-0.6V上升需要200ps 2V下, 上升率0.5ns/V, 速度翻倍 而不是需要上升到1V和需要上升到2V |

acalephs0v0 发表于 2024-6-12 02:12 ddr5的制程比ddr4更先进,所以电压必须降低? |

acalephs0v0 发表于 2024-6-12 02:12 原来如此 是我想当然了 |

| 电压和功耗的关系是平方 |

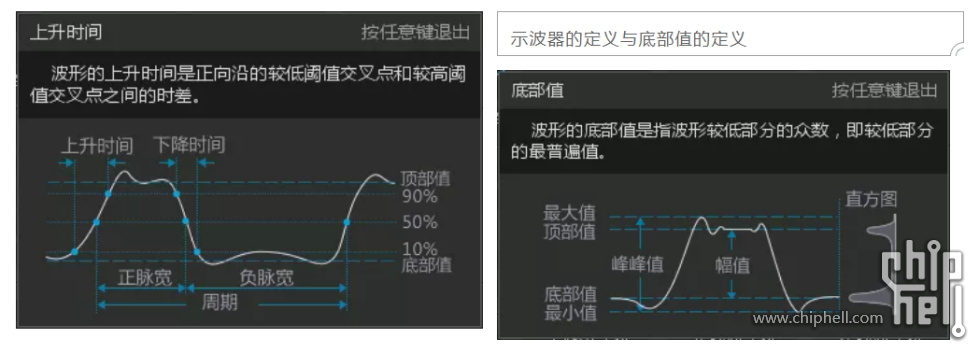

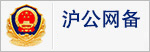

ttt5t5t 发表于 2024-5-16 14:06 错了,同工艺越低电压速度越慢。 电路上升下降时间的计算方式是负载电容乘以电压除以电流,而数字电路的平均电流和电压的平方成正比,所以相乘之后上升下降时间和电压成反比。电压越高电路完成翻转越快。 电压越来越低就是因为换了工艺。一般来讲新工艺会缩短沟道长度,而沟道电场等于电压除以沟道长度,所以必须等比例降低电压,否则沟道电场会过大击穿晶体管。实际上当然更复杂,不过电压总体是随着工艺换代不断下降的。 |

ttt5t5t 发表于 2024-5-16 14:06 ddr6、ddr7的电压是不是会更低  |

信号有上升时间,电流不能突变,IO驱动能力有限,越低的电压上升时间越短,更利于高速变化,功耗也更低。

|

huangfuda 发表于 2024-5-17 14:39 就是从0到1的变化越快越好 越接近方波越好 |

ttt5t5t 发表于 2024-5-16 14:06 快速跳变什么意思 |

| 功耗P=1/2*CV^2f, 所以降低电压能有效降低功耗 |

|

电压低,才能快速跳变 电压低,才能压低功耗 |

|

本帖最后由 猫LOVE 于 2024-5-16 13:56 编辑 电压的作用是保证信号强度,只要电压能保证信号的完整以及信号的纯净,低电压只会比高电压更好,这也是工艺制程进步后的趋势,你会发现以前的老物件电压都高的离谱 |

| 摩尔定律,硅工艺的演进是伴随着工艺线宽减小和工作电压减小,线宽小带来的好处是 单位晶体管成本降低,寄生电容小(频率快),降电压的好处大家都懂,降功耗,大家降压超频玩的那么溜,你就不允许 DDR的定标准的人 也来 降压超频。 对于内存超频玩家,加电压加散热马甲也是常规炒作。 |

imyz 发表于 2024-5-16 11:53 有道理⛄ |

| 以前的CPU还是5V的呢 |

| 处理器也是越来越低的,我是说基准电压。 |

| 能效比当然是越低越好。 |

|

D5的规范标准定的就是1.1V,至于为什么这么定。可以查下JEDEC DDR5标准制定背景。 |

|

猜测一下:工艺越提升,即:纳米数值越小,则越需要低电压,因为硅半导体并不耐高压,为防“击穿”?这是其一; 其二,考虑到电流做电功发热,电流也不能过大,一是高温又将造成材料耐压能力下降,二是线路间“漏电”。在阻抗一定的情况下,降压也降低电流,符合这一要求。 |

| 电压跟容量没有绝对关系啊,电压得益于制程的升级优化、具体细节后面大佬们科普吧 |

Archiver|手机版|小黑屋|Chiphell

( 沪ICP备12027953号-5 ) 310112100042806

310112100042806

GMT+8, 2025-5-22 22:10 , Processed in 0.013701 second(s), 9 queries , Gzip On, Redis On.

Powered by Discuz! X3.5 Licensed

© 2007-2024 Chiphell.com All rights reserved.