zoo 发表于 2022-9-3 11:49 GMI2和DDR4的情况下是一个GMI抵得上双通道的读,或者单通道的写。 但是GMI3和DDR5是一个GMI只抵1.33通道的读,和0.66通道的写。 哪怕24GMI3配12 DDR5,相比之前也只好了33%而已,不算什么非常过剩呀。 |

af_x_if 发表于 2022-9-3 00:17 问题是12通道配24个gmi3真能用上吗?  |

zoo 发表于 2022-9-2 23:53 有也是3组吧,3*8和2*12的总数一样,正好匹配同一个iodie。 |

zoo 发表于 2022-9-2 23:53  我只是猜测一下嘛…… 我只是猜测一下嘛…… |

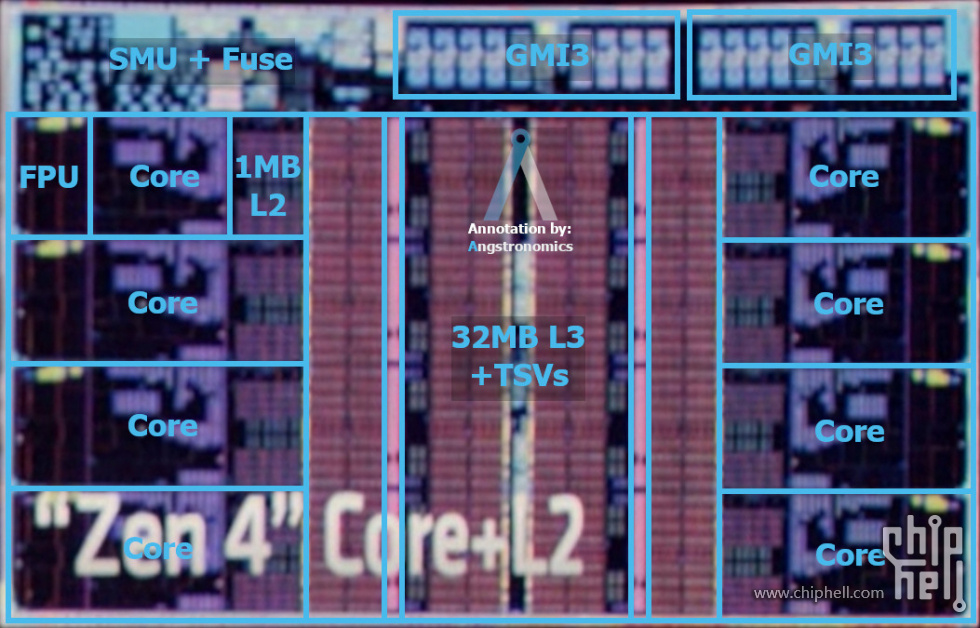

我用第三人称 发表于 2022-9-2 23:17 zen4c的ccd你还没看见过啊,所以不能假设就和zen4一样吧。 |

| 等评测吧,也快来了 |

zoo 发表于 2022-9-2 18:43 单CCD两组GMI3是为Zen4C准备的? |

堕落的翼 发表于 2022-9-2 21:44 AM5不需要吧 AM5的iodie应该是4组GMI的,毕竟这样才能让双CCD芯片里每个CCD都吃满DDR5内存。 |

sevastian 发表于 2022-9-2 21:43    |

af_x_if 发表于 2022-9-2 17:45 那样的话就得准备两种AM5基板了,以AMD的抠法,我感觉够呛,服务器钱多点估计可能 |

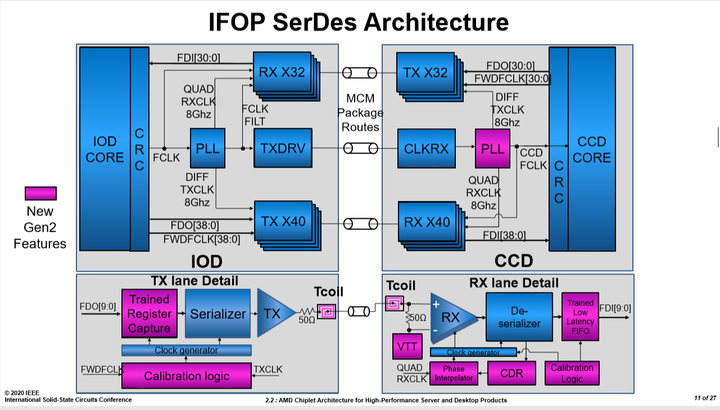

堕落的翼 发表于 2022-9-2 17:23 serdes不需要时钟,又不是同步接口。 我没研究过die shot,如果你说的39实际上是看到了40个,你计算的时候减掉了1,那39的说法有问题。 |

zoo 发表于 2022-9-2 18:43 zoo大来了,我投降了。 (能给我托梦一个5950X3D吗  ) ) |

堕落的翼 发表于 2022-9-2 17:51 靠边了,都快说到点子上了  |

本帖最后由 堕落的翼 于 2022-9-2 19:58 编辑 af_x_if 发表于 2022-9-2 17:45 ……加组肯定是有用处的,虽然肯定有在GMI2基础上拓展的因素,但估计和消费者无关,更和AM4无关。 感觉还是我梦里的5950X3D更现实一些 |

本帖最后由 af_x_if 于 2022-9-2 17:49 编辑 堕落的翼 发表于 2022-9-2 17:23 我觉得不选择组内加频率或者加宽度,而是选择加组,就是为了兼容性。 而兼容性就是为了AM4。芯片照出来前如果AM4版Zen4存在的概率30%,芯片照后就是70%了。 而且我觉得,AM4版Zen4其实会只出单CCD的,但会把两组GMI都用接到IODIE上,这样写入减半的问题也没有了。 |

sevastian 发表于 2022-9-2 02:53 把时钟加上其实挺整的,RX 40 TX 32,比例5:4。 我个人感觉应该所有收发器都应该是用到的,空余带宽用来缓存同步、总线控制和保证延迟、突发性能。 仔细看ZEN 4 CCD dieshot,明显分成了两组,从图上看一组GMI3虽然小了不少收发器的比例和GMI2是一致的(左半边RX 5,右半边TX 4),两组都用上的话即使速率保持fclk*10不变带宽也能翻倍,提升访存速度。两组都用上的话…… |

堕落的翼 发表于 2022-9-1 23:52 我觉得这种零零碎碎的收发器数量,估计要不然是挑出来32/16个时序比较一致的,其他端口都down掉,要不然就是有些端口是用来传递指令突发数据之类的。 考虑到这个线速率,我觉得更可能是有很多端口直接down了。 |

堕落的翼 发表于 2022-9-1 23:52 原来是这样。 |

| 等解禁测试,比较好奇这次的内存性能 |

af_x_if 发表于 2022-9-1 22:16 看上边) |

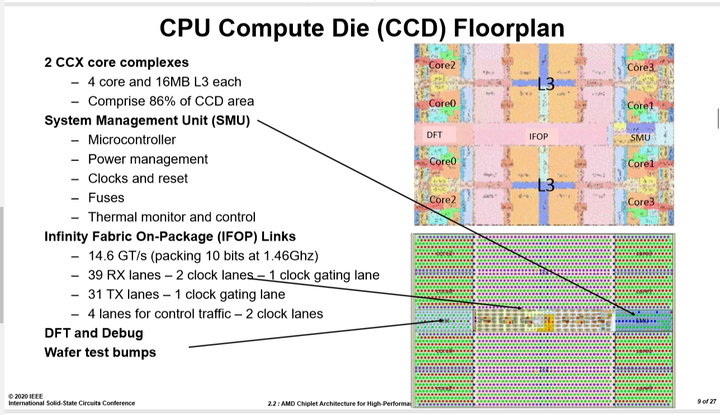

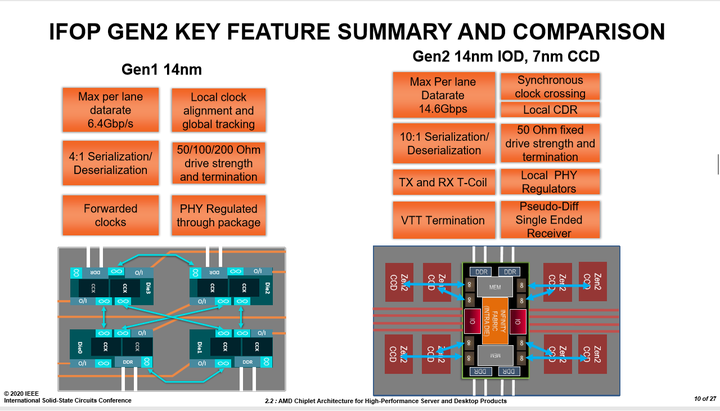

本帖最后由 堕落的翼 于 2022-9-2 00:07 编辑 sevastian 发表于 2022-9-1 21:59 怎么把我上古回答翻出来了……这个东西别看了,写的挺乱的,如果真想看有用的东西直接去找zen 2的isscc幻灯片。 https://www.slideshare.net/AMD/a ... nd-desktop-products 关于内容我澄清一下,也回答一下下面大哥的问题,以下只适用于zen 2和zen 3, zen 4不知道,出处都是isscc的幻灯片,我也懒得放了。 1.GMI到底是啥:SerDes。单端(非差分),上下行不对等,一个CCD一共39条RX,31条TX,四条控制。速率为fclk*10,8/10编码,理论带宽(Bbps) RX:39B*fclk TX:31B*fclk。 2.内存带宽测试写入半速是因为GMI吗:是也不是。 是,因为GMI的下行带宽确实跑不满内存带宽(假定同步fclk=uclk,跑满需要带宽32B*fclk,实际TX带宽只有31B*fclk)。 不是,因为RX带宽虽然不够跑满,但是远没有只有一半速度这么离谱。 至于到底为啥只有一半,我也不知道,估计是fabric上做了QoS控制了写入带宽,gmi上还得有其他控制,缓存同步流量,防止Serdes堵塞,TX带宽39B*fclk的裕量估计也是因为这个。 3.写入砍半啥影响:我觉得没……实际绝大部多数情况肯定是读多写少,内存本质是半双工的所以写入不会到一半。 4.延迟是Serdes造成的吗:不是,主要还是因为fabric。 ZEN 4的GMI到目前为止知之甚少,AMD发布会核心架构图都没给。但从发布会的模糊dieshot和目前所知一些内存跑分 fclk情况可以推测:RX TX条数都增加了,而且内存写入性能有改进。

|

|

fclk X3 =内存频率 |

|

我认为,2组而不是二倍位宽,恰恰就是为了兼容AM4的iodie。 大不了1组空着嘛。 |

sevastian 发表于 2022-9-1 21:59 都32bit了还怎么serdes,又不是x32。 |

| 谁给翻译翻译,,,, |

|

本帖最后由 sevastian 于 2022-9-1 22:13 编辑 gmi用的是serdes吗?难怪会有这么高延迟。 找了一个20年的分析,原来是8b/10b的serdes,还是单端信号,这玩意是怎么跑到19GT/s的,真是奇迹。 为何AMD Matisse CPU 内存写入效能有差异? - 阮平的回答 - 知乎 https://www.zhihu.com/question/414468853/answer/1410871501 |

lh4357 发表于 2022-9-1 21:43 八月初听林大说Zen4临上市突然让板厂锁一个叫啥64bit的东西,不知道啥用意 |

zoo 发表于 2022-9-1 21:37 跑缓存一致多少需要点带宽 所以处理器带宽比内存带宽略大些还是对的 |

| 另一组gmi会不会是隐藏款ddr4通道? |

Archiver|手机版|小黑屋|Chiphell

( 沪ICP备12027953号-5 ) 310112100042806

310112100042806

GMT+8, 2025-6-18 12:27 , Processed in 0.013889 second(s), 9 queries , Gzip On, Redis On.

Powered by Discuz! X3.5 Licensed

© 2007-2024 Chiphell.com All rights reserved.